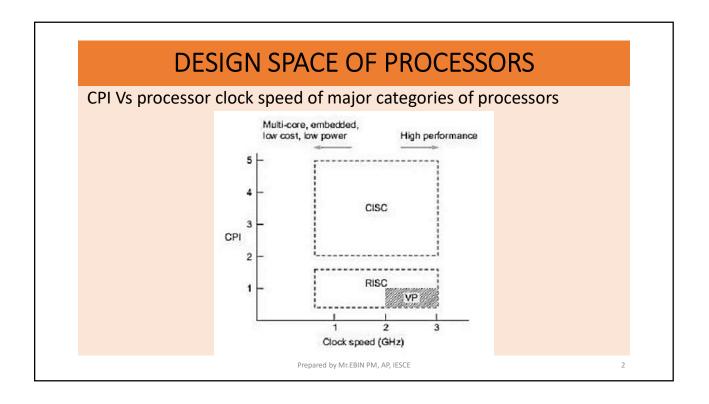

Processor families can be mapped onto a coordinated space of clock rate versus cycles per instruction(CPI)

Under both CISC and RISC categories, products designed for multi-core chips, embedded applications, or for low cost / low power consumption, tend to have lower clock speeds.

High performance processors must designed to operate at high clock speeds.

VP indicate Vector Processor

processors like the Intel Pentium, M68040, older VAX/8600, IBM 390 are known as Complex-instruction-set computers (CISC)

| Architectural<br>Characteristic               | Complex Instruction Set<br>Computer (CISC)                                                                           | Reduced Instruction Set<br>Computer (RISC)                                                       |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Instruction-set size and instruction formats  | Large set of instructions with<br>variable formats (16–64 bits<br>per instruction).                                  | Small set of instructions with<br>fixed (32-bit) format and most<br>register-based instructions. |

| Addressing modes                              | 12-24.                                                                                                               | Limited to 3-5.                                                                                  |

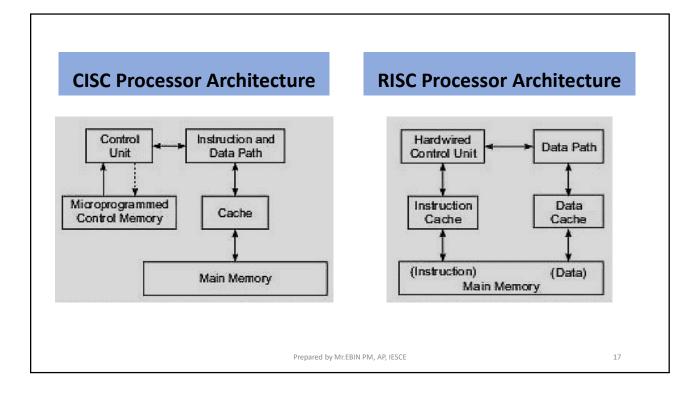

| General-purpose registers<br>and cache design | 8–24 GPRs, originally with a<br>unified cache for instructions<br>and data, recent designs also<br>use split caches. | Large numbers (32–192) of<br>GPRs with mostly split data<br>cache and instruction cache.         |

| СЫ                                            | CPI between 2 and 15.                                                                                                | One cycle for almost all instruction<br>and an average CPI < 1.5.                                |

| CPU Control                                   | Earlier microcoded using control<br>memory (ROM), but modern<br>CISC also uses hardwired control.                    | Hardwired without control memory                                                                 |

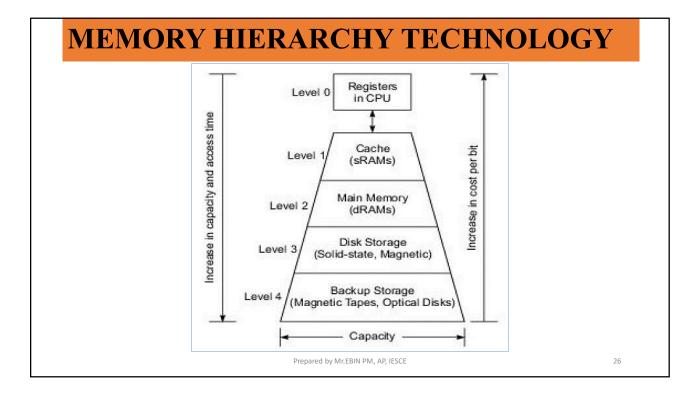

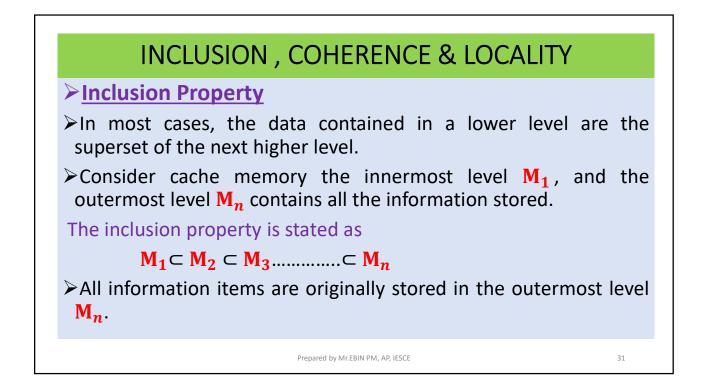

- During the processing, subsets of  $M_n$  are copied into  $M_{n-1}$ . Similarly subset of  $M_{n-1}$  are copied in to  $M_{n-2}$  and so on.

- In other words, if an information word is found in  $M_i$  then copies of the same word can also be found in all upper levels  $M_{i+1}$ ,  $M_{i+2}$ , ... $M_n$ .

- The highest level is the backup storage, where everything can be found.

- Information transfer between the CPU and cache is in terms of words (4 or 8 bytes each depending on the word length of a machine).

- The cache is divided into cache blocks. Blocks are the units of data transfer between the cache and main memory, or between  $L_1$  and  $L_2$  cache

Prepared by Mr.EBIN PM, AP, IESCE

32

| Coherence Property                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| • The coherence property requires that copies of the same information item at successive memory levels be consistent                    |

| • If a word is modified in the cache, copies of that word must be updated immediately or eventually at all higher levels                |

| • Frequently used information is often found in the lower levels in order to minimize the effective access time of the memory hierarchy |

| • There are two strategies for maintaining the coherence in a memory hierarchy.                                                         |

| write-through (WT)                                                                                                                      |

| write-back (WB)                                                                                                                         |

|                                                                                                                                         |

| Prepared by Mr.EBIN PM, AP, IESCE 33                                                                                                    |

- write-through (WT) which demands immediate update in M<sub>i+1</sub> if a word is modified in M<sub>i</sub>, fori= 1,2,....,n-1

- write-back (WB) which delays the update in  $M_{i+1}$  until the word being modified in  $M_i$  is replaced or removed from  $M_i$

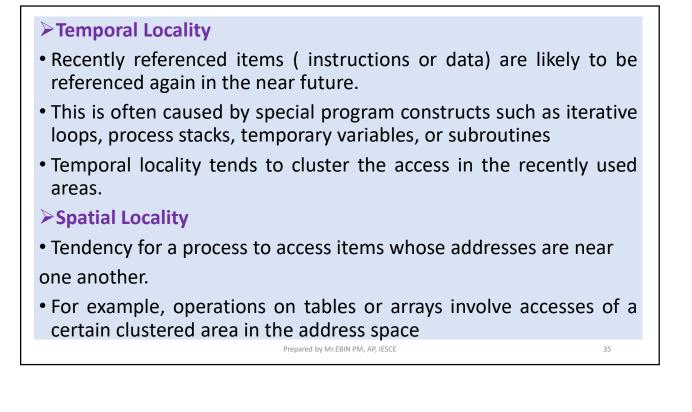

## Locality of Reference

- The memory hierarchy was developed based on a program behavior known as locality of reference.

- Memory references are generated by the CPU for either instruction or data access

- The same value or related storage locations are frequently accessed depending on the memory access pattern

- The three dimensions of the locality property are temporal, spatial and sequential. Prepared by Mr.EBIN PM, AP, IESCE 34

## <section-header><list-item><list-item><list-item><list-item><list-item><table-row><table-row><table-row></table-row></table-row>